THE UNIVERSITY OF BRITISH COLUMBIA

Department of Electrical and Computer Engineering

**ELEC 401 – Analog CMOS Integrated Circuit Design**

**Final Exam**

**Due: Wednesday, December 9<sup>th</sup>, 2020 at 8:30 am (Pacific Time)**

This is an open book take-home exam and calculators are allowed. Please attempt to answer all problems. A blank sheet will not receive any marks! Please do not consult and/or discuss the questions and/or your solutions with anyone except the instructor. Your solutions/answers should be based on your individual effort! Please also note that each question has its own transistor parameters.

**Good luck!**

**This exam book including the cover page consists of 16 pages. Please check that you have a complete copy. You may use both sides of each sheet if needed.**

Surname \_\_\_\_\_

First name \_\_\_\_\_

Student Number \_\_\_\_\_

| #            | MAX        | GRADE |

|--------------|------------|-------|

| 1            | 20         |       |

| 2            | 20         |       |

| 3            | 20         |       |

| 4            | 20         |       |

| 5            | 20         |       |

| <b>TOTAL</b> | <b>100</b> |       |

**READ THIS**

IMPORTANT NOTE:

*Candidates guilty of any of the following, or similar, dishonest practices shall be liable to disciplinary action:*

*Speaking or communicating with other candidates or non-candidates regarding the exam questions.*

*Purposely exposing their solution to the view of other candidates.*

*The plea of accident or forgetfulness shall not be received.*

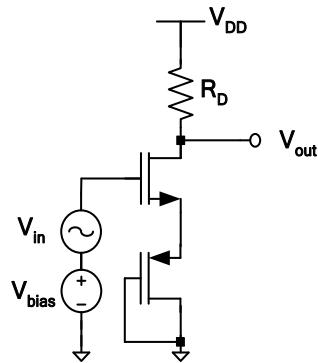

1. In the following circuit, assuming the NMOS transistor is operating in the saturation region:

Assume  $\lambda_{NMOS} = \lambda_{PMOS} = 0$ ,  $\gamma_{NMOS} = 0.5 \text{ V}^{1/2}$ ,  $\gamma_{PMOS} = 0 \text{ V}^{1/2}$ ,  $V_{TH0(NMOS)} = 0.4 \text{ V}$ ,  $V_{TH0(PMOS)} = -0.6 \text{ V}$ ,  $\mu_n C_{ox} = 1 \text{ mA/V}^2$ ,  $\mu_p C_{ox} = 500 \mu\text{A/V}^2$ ,  $(W/L)_{NMOS} = 80$ ,  $(W/L)_{PMOS} = 50$ , and  $V_{DD} = 3 \text{ V}$ .

a) Find the required  $V_{bias}$  for which the dc bias current of the circuit is 0.5 mA. [5 marks]

**Note:** Please pay attention to  $\gamma$  for the NMOS and the PMOS transistor.

Write your answer in this box

$$V_{bias} = \underline{\hspace{2cm}} \text{ V}$$

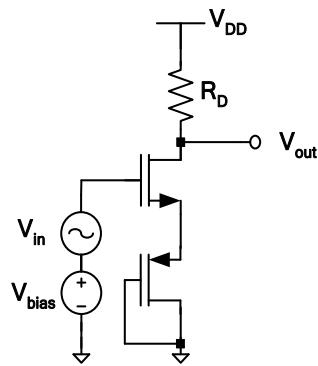

b) If  $R_D = 0.2 \text{ k}\Omega$ , find the small-signal gain of the circuit.

For your convenience the circuit and its parameters are duplicated below:

$\lambda_{\text{NMOS}} = \lambda_{\text{PMOS}} = 0$ ,  $\gamma_{\text{NMOS}} = 0.5 \text{ V}^{1/2}$ ,  $\gamma_{\text{PMOS}} = 0 \text{ V}^{1/2}$ ,  $V_{\text{TH0(NMOS)}} = 0.4 \text{ V}$ ,  $V_{\text{TH0(PMOS)}} = -0.6 \text{ V}$ ,  $\mu_n C_{\text{ox}} = 1 \text{ mA/V}^2$ ,  $\mu_p C_{\text{ox}} = 500 \mu\text{A/V}^2$ ,  $(W/L)_{\text{NMOS}} = 80$ ,  $(W/L)_{\text{PMOS}} = 50$ , and  $V_{\text{DD}} = 3 \text{ V}$ . [5 marks]

Write your answer in this box

$$A_v = \text{_____ V/V}$$

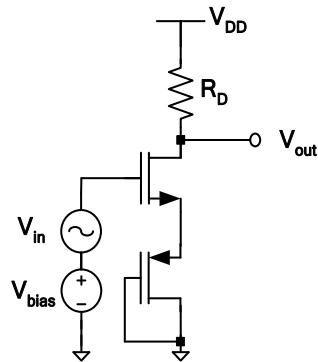

c) Find  $R_D$  such that the magnitude of the small-signal gain of the circuit is 10.

For your convenience the circuit and its parameters are duplicated below:

$\lambda_{NMOS} = \lambda_{PMOS} = 0$ ,  $\gamma_{NMOS} = 0.5 \text{ V}^{1/2}$ ,  $\gamma_{PMOS} = 0 \text{ V}^{1/2}$ ,  $V_{TH0(NMOS)} = 0.4 \text{ V}$ ,  $V_{TH0(PMOS)} = -0.6 \text{ V}$ ,  $\mu_n C_{ox} = 1 \text{ mA/V}^2$ ,  $\mu_p C_{ox} = 500 \text{ } \mu\text{A/V}^2$ ,  $(W/L)_{NMOS} = 80$ ,  $(W/L)_{PMOS} = 50$ , and  $V_{DD} = 3 \text{ V}$ . **[5 marks]**

Write your answer in this box

$$R_D = \text{_____ } \Omega$$

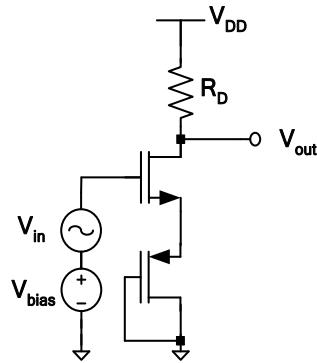

d) **Designer X** would argue with you that the value of  $R_D$  that you have calculated in part (c) is not a good engineering choice and the gain of your circuit would not be as expected. Please state your reason whether or not you agree with **Designer X**? [5 marks]

For your convenience the circuit and its parameters are duplicated below:

$\lambda_{NMOS} = \lambda_{PMOS} = 0$ ,  $\gamma_{NMOS} = 0.5 \text{ V}^{1/2}$ ,  $\gamma_{PMOS} = 0 \text{ V}^{1/2}$ ,  $V_{TH0(NMOS)} = 0.4\text{V}$ ,  $V_{TH0(PMOS)} = -0.6\text{V}$ ,  $\mu_n C_{ox} = 1 \text{ mA/V}^2$ ,  $\mu_p C_{ox} = 500 \text{ }\mu\text{A/V}^2$ ,  $(W/L)_{NMOS} = 80$ ,  $(W/L)_{PMOS} = 50$ , and  $V_{DD} = 3\text{V}$ .

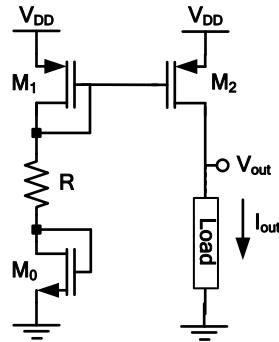

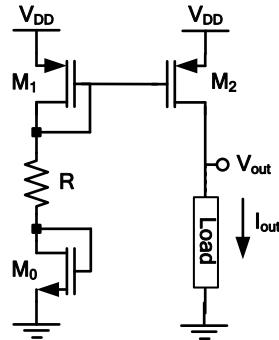

2. In the following circuit assume that:

$\lambda_{(NMOS)} = \lambda_{(PMOS)} = 0 \text{ V}^{-1}$ ,  $\gamma = 0$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $V_{TH(NMOS)} = |V_{TH(PMOS)}| = 0.5 \text{ V}$ ,  $\mu_n C_{ox} = 1 \text{ mA/V}^2$ , and  $\mu_p C_{ox} = 0.25 \text{ mA/V}^2$ .

Furthermore, assume all transistors have the same size and  $M_2$  is operating in saturation. Given that  $R = 1.7 \text{ k}\Omega$  and  $I_{out} = 1 \text{ mA}$

- Find the aspect ratio of transistor  $M_0$ , i.e.,  $(W/L)_0$ ? [15 marks]

- What is the maximum voltage of  $V_{out}$  for which  $M_2$  remains in saturation region? [5 marks]

For your convenience the circuit diagram and transistor parameters are replicated here:

$\lambda_{(NMOS)} = \lambda_{(PMOS)} = 0 \text{ V}^{-1}$ ,  $\gamma = 0$ ,  $V_{DD} = 3.3 \text{ V}$ ,  $V_{TH(NMOS)} = |V_{TH(PMOS)}| = 0.5 \text{ V}$ ,  $\mu_n C_{ox} = 1 \text{ mA/V}^2$ , and  $\mu_p C_{ox} = 0.25 \text{ mA/V}^2$ .

Furthermore, assume all transistors have the same size and  $M_2$  is operating in saturation. Assuming that  $R = 1.7 \text{ k}\Omega$  and  $I_{out} = 1 \text{ mA}$

Write your answer in this box

$$(W/L)_0 = \underline{\hspace{2cm}}$$

Write your answer in this box

$$V_{out,max} = \underline{\hspace{2cm}} \text{ V}$$

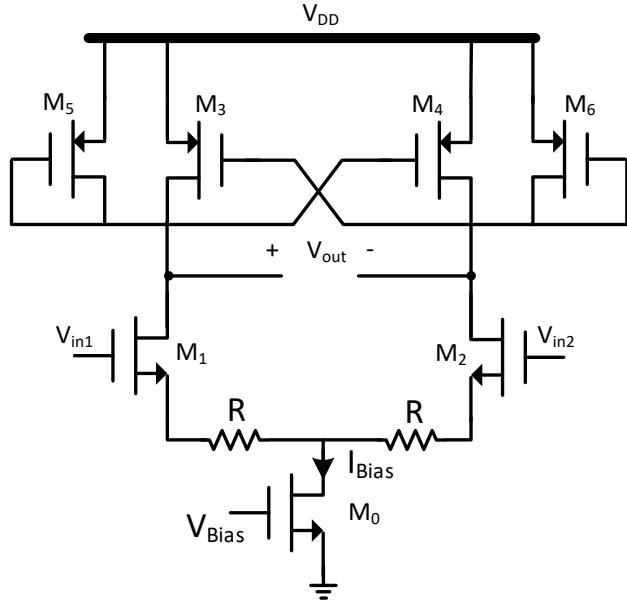

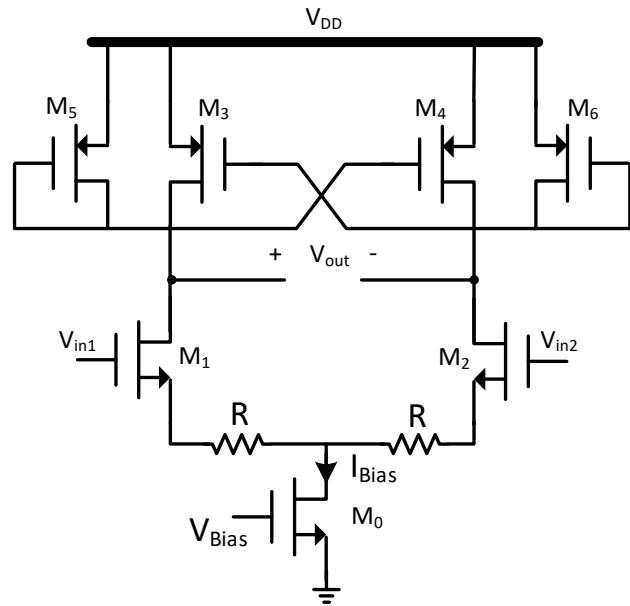

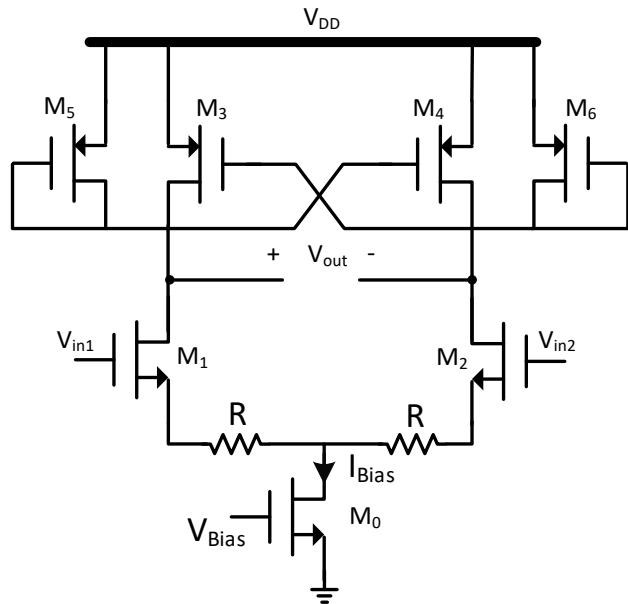

3. In the following symmetric circuit, assume all transistors are operating in saturation region,  $\lambda = 0$ , and  $\gamma = 0$ . [20 marks]

- Find the small-signal differential voltage gain of the circuit, i.e.,  $V_{out}/(V_{in1}-V_{in2})$ , in terms of transconductances of the relevant transistors and  $R$ .

- What is the small-signal differential voltage gain if  $(W/L)_5=2\times(W/L)_3$ ,  $(g_{m1})\times R = 1$ , and  $(W/L)_1=2\times(W/L)_3$ ?

- Given that  $M_5$  and  $M_3$  have the same effective voltage, find the relationship between  $(W/L)_5$  and  $(W/L)_3$  so that the maximum small-signal differential gain of the circuit is achieved. What is the value of this maximum gain?

For your convenience the circuit and the assumptions and circuit parameters are duplicated below:

For your convenience the circuit and the assumptions and circuit parameters are duplicated below:

Expression for Differential gain = \_\_\_\_\_

Value of differential gain = \_\_\_\_\_

Relation between  $(W/L)_5$  and  $(W/L)_3$  for maximum gain = \_\_\_\_\_

Maximum gain = \_\_\_\_\_

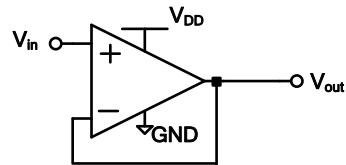

4. Find the required phase margin for an op-amp such that when it is configured in a unity-gain feedback (shown below), the magnitude frequency response of the closed-loop system shows no peaking (i.e., 0% peaking) at the gain crossover frequency (i.e., at the frequency where the magnitude of the open-loop gain of the opamp is 1)? **[20 marks]**

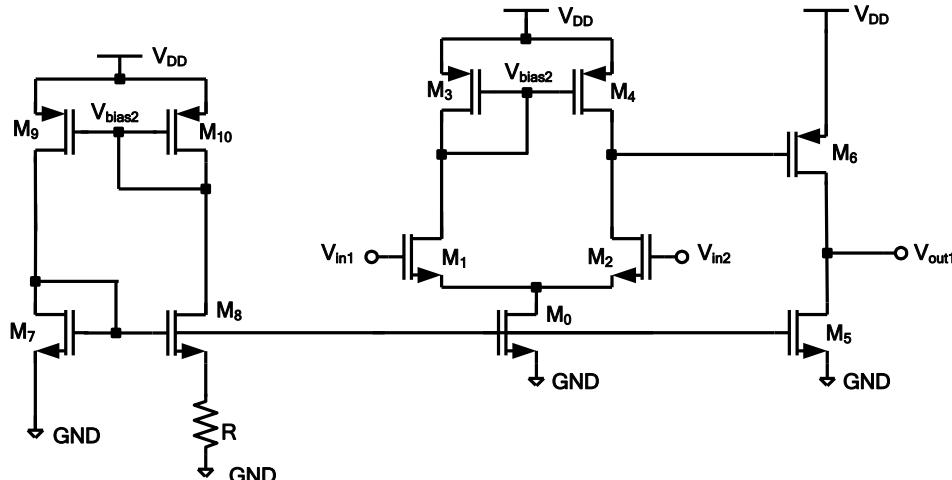

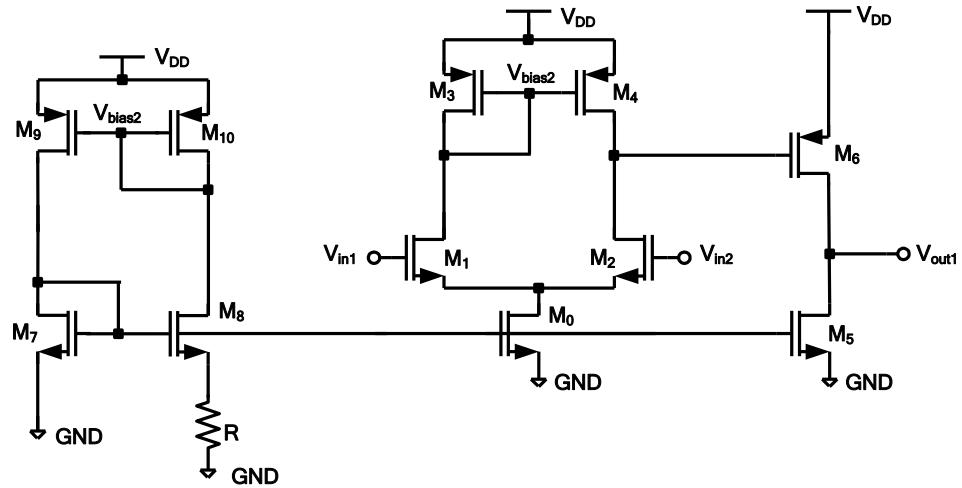

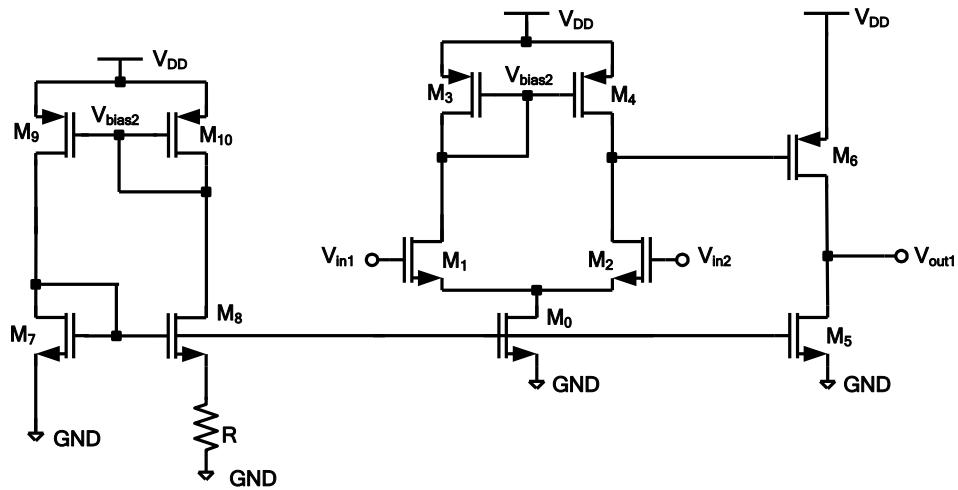

5. Design a two-stage op-amp based on the topology shown below with the following design specifications (Note that the gate of  $M_{10}$  is also connected to the gate of  $M_3$ ):

- $V_{DD}=1$  V

- Total power consumption of 1 mW

- Total gain of 8000

- $L=0.2$   $\mu$ m for all the devices

- $W_9=W_{10}$

- $W_8=4W_7$

- $R=1$  k $\Omega$

Use the following assumptions for your design

- The differential stage is symmetric

- The bias currents of the first and second stage are equal (i.e.,  $I_0=I_5$ ) and  $I_{10}$  is 0.1 mA.

- The magnitude of overdrive voltages of  $M_4$ ,  $M_5$ , and  $M_6$  are equal

The technology parameters are:

$$\lambda_{(NMOS)}=\lambda_{(PMOS)}=0.05V^{-1}, \gamma = 0, V_{DD}=1V, V_{TH(NMOS)}=|V_{TH(PMOS)}|=0.4V, \mu_nC_{ox}=1 \text{ mA/V}^2, \mu_pC_{ox}=0.5 \text{ mA/V}^2.$$

**Note:** Use the parameter  $\lambda$  only for calculating the  $r_o$  of the transistors. **Do not** use  $\lambda$  (that is assume  $\lambda = 0$ ) in any other calculation including for calculating bias currents.

- Find the widths of all transistors (namely,  $W_0, W_1, W_2, W_3, W_4, W_5, W_6, W_7, W_8, W_9, W_{10}$ ). **[12 marks]**

- What is the maximum peak-to-peak swing of the output signal? **[4 marks]**

- Assuming that we have the maximum output swing (output is a symmetrical sinusoidal signal), what should be the output common-mode level (i.e., the DC level of the output signal for maximum swing)? **[4 marks]**

For your convenience the circuit diagram and transistor parameters is replicated here:

$\lambda_{(NMOS)}=\lambda_{(PMOS)}=0.05V^{-1}$ ,  $\gamma = 0$ ,  $V_{DD}=1V$ ,  $V_{TH(NMOS)}=|V_{TH(PMOS)}|=0.4V$ ,  $\mu_n C_{ox}=1 \text{ mA/V}^2$ ,

$\mu_p C_{ox}=0.5 \text{ mA/V}^2$ .

For your convenience the circuit diagram and transistor parameters is replicated here:

$\lambda_{(NMOS)}=\lambda_{(PMOS)}=0.05V^{-1}$ ,  $\gamma = 0$ ,  $V_{DD}=1V$ ,  $V_{TH(NMOS)}=|V_{TH(PMOS)}|=0.4V$ ,  $\mu_n C_{ox}=1 \text{ mA/V}^2$ ,  $\mu_p C_{ox}=0.5 \text{ mA/V}^2$ .

$$W_0 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_1 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_2 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_3 = \underline{\hspace{2cm}} \mu\text{m},$$

$$W_4 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_5 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_6 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_7 = \underline{\hspace{2cm}} \mu\text{m},$$

$$W_8 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_9 = \underline{\hspace{2cm}} \mu\text{m}, \quad W_{10} = \underline{\hspace{2cm}} \mu\text{m},$$

$$\text{Maximum peak-to-peak output swing} = \underline{\hspace{2cm}} \text{V}, \quad \text{Output DC level} = \underline{\hspace{2cm}}$$

This page is intentionally left blank.