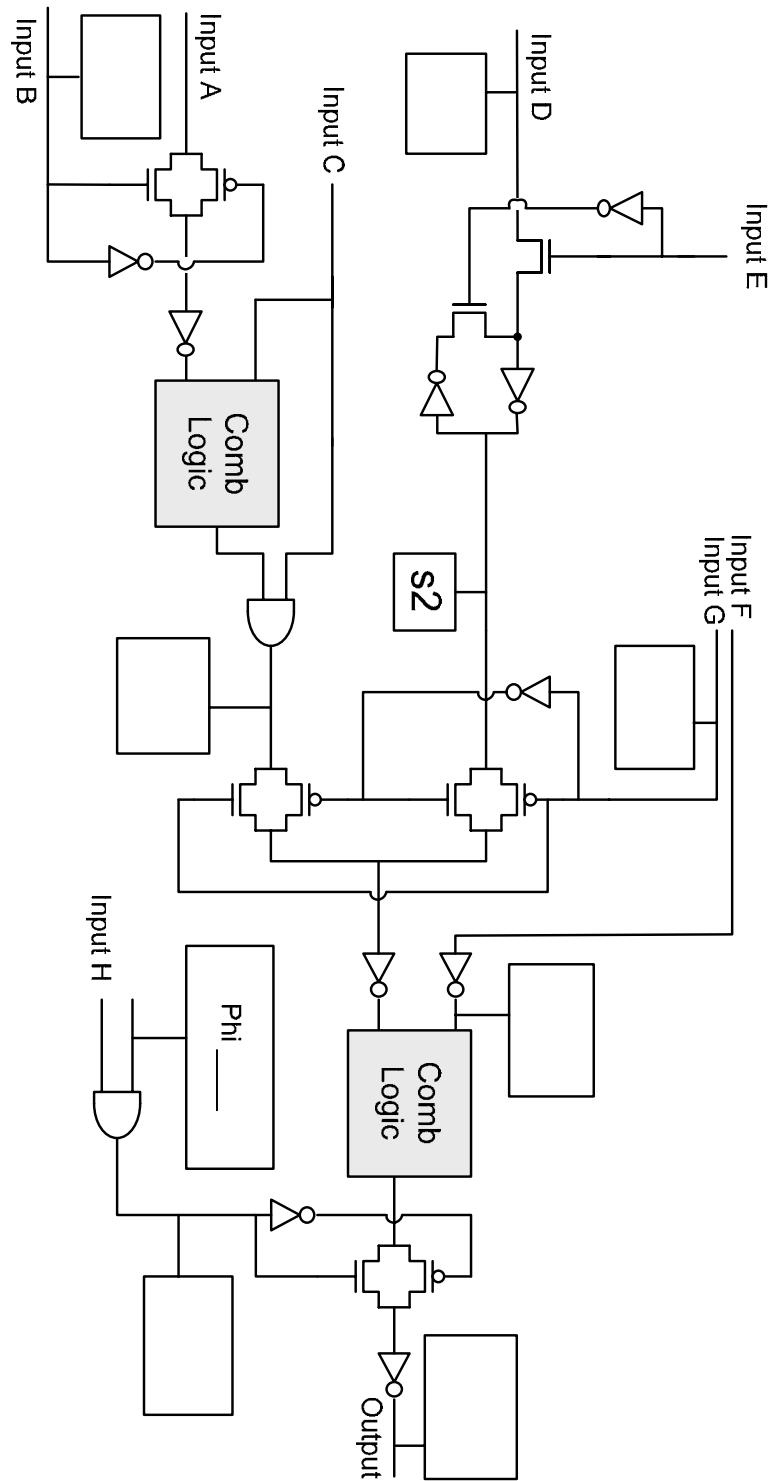

Consider the following two-phase clocked circuit. Using the labeling convention discussed in class, **fill in each box below with one of: s1, s2, q1, q2, v1, v2, phi1, or phi2** depending on the timing type of the corresponding signal. One of the signals has been labeled as having type s2 for you; this is the place to start.

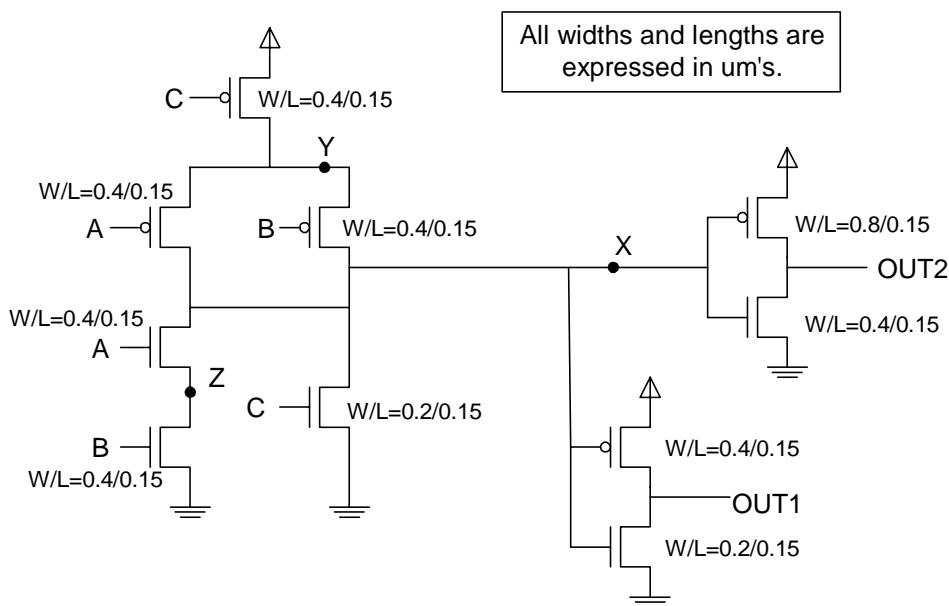

Answer the following questions regarding the circuit below. You might find these numbers useful (you may not need all of them). Note this technology is different than the one in class. You should use this new technology.

$$\lambda = 0.06 \mu\text{m} \text{ (so the minimum transistor length is } 0.12 \mu\text{m)}$$

$$C_{gate} = 1.4 \text{ fF}/\mu\text{m of transistor width}$$

$$C_{ndiff} = 1.2 \text{ fF}/\mu\text{m of transistor width}$$

$$C_{pdiff} = 1.0 \text{ fF}/\mu\text{m of transistor width}$$

$$R_{on,n} = 12 \text{ K}\Omega * L/W$$

$$R_{on,p} = 24 \text{ K}\Omega * L/W$$

$$V_{dd} = 1.2 \text{ volts}$$

Also assume the layout engineer for this gate wasn't very smart (clearly not from UBC) and so he/she did not share diffusion regions between transistors (so every transistor has its own source/drain region).

Assume the following nodes have the following initial voltage:

Node Z: initial voltage = 0 volts

Node Y: initial voltage = 1.2 volts

Node X: initial voltage = 1.2 volts

Also assume the inputs initially have the following voltages:

Input A: initial voltage = 0 volts

Input B: initial voltage = 1.2 volts

Input C: initial voltage = 0 volts

Suppose Input A switches from 0 Volts to 1.2 Volts. Clearly, Node X will fall. On the next page, work out the delay until Node X reaches 0.6 Volts ( $V_{dd}/2$ ). Show your work!